Fixing a Poorly Commodore 64 (Part 2)

In the previous post I’d checked the DRAM and the MOS logic chips, some of which are responsible for memory decoding. The RAM was fine, and one of the logic chips had failed. I was, however, still seeing what looked like an anomalous signal on some of the address lines.

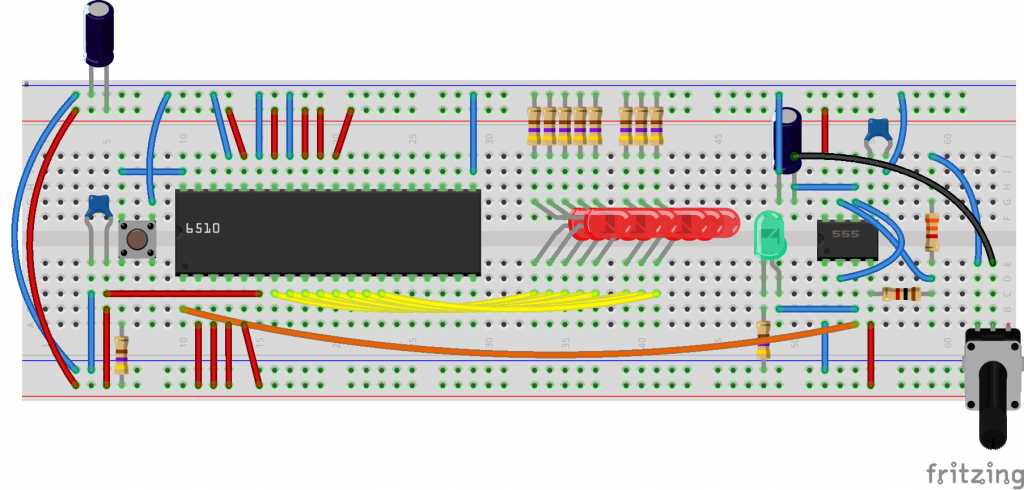

I couldn’t think of an easy way to diagnose the 6510 CPU in situ, so decided to desolder it from the motherboard and test on a breadboard in a NOP test circuit.

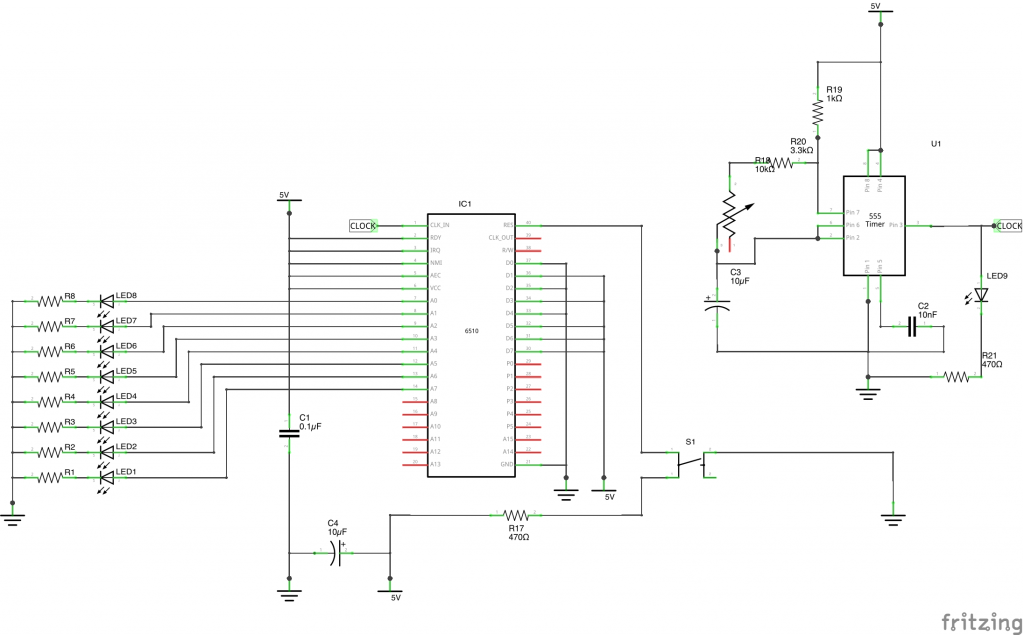

The principle behind the NOP test circuit is fairly simple:

- Provide the 6510 CPU with 5V

- Feed it a clock signal – square wave provided by a 555 timer

- Hard code the control pins RDI, IRQ, NMI and AEC

- Hard code a NOP (No Operation) instruction on the data lines; for 6502/6510 this is 0xEA

- Wire some LEDs to the address lines for output

The NOP instruction is chosen because all it does is increment the program counter to the next address.

I’d already built a circuit to do a NOP test on a Z80 which could be easily modified to test a 6510.

It’s worth noting that whilst the 6510 is a 6502 variant, it is not pin compatible, so you will need to adapt the circuit if you want to test a 6502.

The 6510 starts at the address pointed to by the reset vector (address 0xFFFC and 0xFFFD). As the data bus is hard-coded with the byte 0xEA, this will mean the 6502 will start at 0xEAEA, and continue executing NOP instructions until it is powered off, wrapping round back to 0x0000 when the program counter reaches 0xFFFF.

The program counter value will be output on the address lines of the CPU, so the LEDs wired to the least significant 8 bits of the address line (A7-A0) will appear to count in binary if the CPU is working.

Anyway, the CPU in question works just fine, so the next step may be to reassemble the board, replacing the MOS logic with modern 74 series logic chips, and seeing whether it will boot up. There is one essential chip that has not been tested, the PLA, which is a combinational logic chip that implements the memory map of the C64; this is another chip that is prone to failure.